The most important numbers

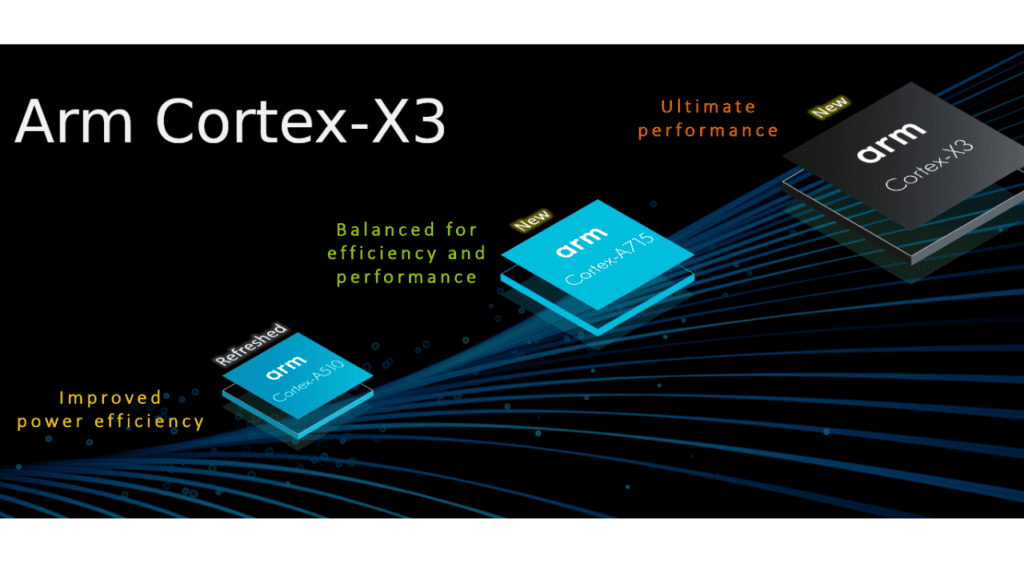

If you’re looking for a quick summary of what to expect in the coming year, consider these crucial figures. Arm’s Cortex-X3 high-performance CPU core follows on from the Cortex-X2 and X1 generations. As a result, the goal is to perform at the highest level possible. According to Arm, the Cortex-X3 outperforms the Cortex-X2 by 11% when using the identical process, clock speed, and cache configuration (also known as ISO-process). However, when we take into account the predicted improvements from the transition to 3nm manufacturing methods, this gain rises to 25%. With up to a 34% increase in performance over a mid-tier Intel i7-1260P, Arm expects the core to reach even further into the laptop market. In terms of performance, the Cortex-X3 isn’t going to be able to compete with Apple’s M1 and M2. As a result, Arm’s larger, larger, and smaller CPU portfolio will be optimised to its full potential. As well as improving peak and sustained performance, we want to increase the power efficiency of cores that aren’t actively working. However, how exactly did Arm accomplish this?

A few points to keep in mind before diving into the micro-architecture changes of the X3:

Just like its predecessor, the Cortex-X3 is based on Arm’s 64-bit AArch64 architecture. Now that AArch32 support for older architectures has been dropped, Arm claims it has turned its attention to improving the design. Because it uses the same Armv9 architecture as the Cortex-X2, the Cortex-X3 is backwards-compatible with the Cortex-X2. Improved branch prediction accuracy and reduced latency are only two of the many front-end benefits of the new dedicated structure for indirect branches (branches with pointers). In order to profit from Arm’s branch prediction algorithms, the Branch Target Buffer (BTB) has risen dramatically. The L1 BTB cache capacity has been increased by 50%, while the L0 BTB cache capacity has been increased by 10x. As a result of the latter, the core is able to gain performance under workloads where the BTB is frequently encountered. The overall size of BTB necessitated Arm to incorporate a third L2 cache level.

A Branch Predictor and a Branch Target Buffer are two different things

As a means of increasing the number of execution units in the CPU, branch predictors are designed to anticipate incoming instructions within code loops and ifs (branches). It’s faster to predict these instructions ahead of time rather than obtaining them from memory on demand, especially in out-of-order CPU cores With the huge BTB, Arm has also made it possible for the predictor to acquire more instructions earlier in the process. Once again, this contributes to the goal of cutting down on the amount of instruction stalls in the instruction pipeline. For anticipated taken branches, Arm claims an average reduction in latency of 12.2 percent, with a 3 percent reduction in front-end delays, and a 6 percent reduction in mispredictions per thousand branches, as a result.

Find Out More About This Subject

Samsung may be developing a foldable phone for less than $800, but don’t hold your breath. To change the language on an Android device, follow these instructions The micro-op (decoded instruction) cache has also been reduced in size and made more efficient. In comparison to the X2 version, it has been reduced in size by 50%, bringing it back to the same 1.5K entries as the original X1. Arm has also been able to lower the total pipeline depth from 10 to nine cycles by using a smaller mop-cache, which reduces the cost when branch mispredicts occur and the pipeline flushes. TLDR: When instructions reach the execution engine, they run faster and more efficiently because of improved accuracy in branch prediction, larger caches, and a smaller penalty for incorrect predictions.

Defintion: What exactly is a CPU stall/bubble?

When a CPU receives an instruction, it first decodes it, then executes it, then writes back the result. When no instructions are in the pipeline, a stall or bubble develops, wasting a CPU clock cycle. Even so, Arm hasn’t completely rewritten the core, although in smaller increments. To handle spatial and pointer/indirect access patterns, two extra data prefetch engines have been added to the back-end to increase the number of 32-byte integer loads each cycle. As a result, the backend is wider and faster as well. Evolutionary Arm Cortex-X3 Cortex-X2 \sCortex-X1 3.3GHz 3.0GHz 3.0GHz is the anticipated mobile clock speed. Instructions can be sent out in a width of 6 5 5 Length of the instruction pipeline 9 10 11 OoO Execution window: 640 (2x 320) 576 (2x 288) 448 (2x 224) There are various types of execution units In total, there are six ALUs (4 SX and 2 MX). 2 SX and 2 MX ALU 4-Aluminum (two SX and two MX) Cache l1 L2 cache of 64 KByte size

Each of the following is equal to one million bytes:

Tables like the one above can help us understand some of the larger trends. Cortex-X1 and X3 have both increased the OoO window size and number of execution units in order to expose better parallelism, however the pipeline depth was reduced to lower the performance penalty for prediction mismatches between these two generations of Arm processors. In addition to pushing for more powerful CPU designs, Arm is also pushing for more efficient ones this generation, with a focus on front-end improvements.

Depth dive with the Arm Cortex-A715

Compared to the X-series, Arm’s Cortex-A715 outperforms the previous-generation Cortex-A710 in terms of performance and power consumption. In terms of performance, Arm claims the A715 is on par with the older Cortex-X1 core when configured with the exact same clock and cache as the Cortex-X1. The A715’s advancements are concentrated in the front end, like the Cortex-X3. The branch prediction accuracy has been increased as well, with a doubling of the branch prediction capacity and improved algorithms for branch history. As a result, the execution cores perform better and are more efficient, with a 5% reduction in incorrect predictions. Conditional branches can now be supported with two branches per cycle and a three-stage prediction pipeline, which reduces latency. Overall, Arm’s Cortex-A715 is a more compact version of the A710. Optimizing the front and back ends of the processor offers a slight performance boost, but the real benefit is in reducing power consumption. The Cortex-A715 is more efficient than ever before, which is good news for battery life. Nevertheless, it’s also possible that the design has reached the end of its useful life and Arm will require a more significant redesign in order to boost middle-core performance in the future.

What does the refresh of the arm cortex x3 vc cortex a715 mean?

The Cortex-A510 and its companion DSU-110 have been updated by Arm, despite the lack of a new Armv9 core being announced by Arm. The new A510 has a power reduction of up to 5% and timing enhancements that lead to frequency optimizations thanks to the new design. Smartphones will be a little more efficient in low-power applications next year as a drop-in replacement. An interesting twist is that, unlike its predecessor, the redesigned A510 may be configured with AArch32 support for use in legacy mobile and IoT applications as well. As a result, Arm’s partners now have more freedom in how they use the core.

It is now possible to use Arm’s Dynamic Shared Unit (DSU). With up to 12 cores and 16MB L3 cache in a single cluster. Making it suitable for larger and more demanding applications. In laptop and PC products, Arm expects to see a 12-core arrangement with eight big cores and four medium cores. Arm’s partners may also allow us to see processors with more than eight cores on mobile devices. By decreasing software overheating, the DSU-110 enhances communication between connected CPU cores and accelerators. Although this is less relevant to mobile devices, server markets are expected to benefit from this. Also Read: Detailed Brief About the AMD 6 core Ryzen 7000 CPU macOS 13 Ventura: 4 features maddeningly not supported by Intel macs M.2 SSD vs nvmi SSD: What’s the best type of PC storage Chrome OS update automatically brings photos from Android to your Chromebook

Q1: What applications use the arm cortex x3 vc cortex a715 processor?

With the Cortex-M3 CPU, a wide range of devices, from microcontrollers. To automobile body systems to industrial control panels to wireless networking and sensors. Can benefit from strong performance at a cheap cost.

Q2: Is arm cortex x3 vc cortex a715, or just a CPU?

Mid-range application CPU Cortex A55 is built on Arm DynamicIQ technology. A low-cost alternative to high-end GPUs, Arm’s Mali-G68 GPU utilises the Mali Valhall architecture.

Q3: What does the term “cortex” in ARM stands for what?

Arm Holdings licences the ARM Cortex-M family of 32-bit RISC ARM processor cores. They have been used in tens of billions of consumer gadgets because of their low cost and energy efficiency.

Q4: The ARM Cortex-M3 is a part of what?

Simply said, the Arm Cortex-M3 processor. Real-time, high performance, and complex operations may all be handled by the Arm Cortex M3 core processor. Which has a 32-bit architecture. Arm Cortex-M3 microcontrollers are scalable and cost-effective, making them ideal for a wide range of applications.

Q5: Is ARM Cortex M3 a microcontroller or a processor?

Real-time microcontroller programming on ARM Cortex M3 processors in embedded and low-cost platforms including industrial control systems. Automobile body systems, wireless networking and sensors, and so on, is a great fit for this processor.

Q6: What is the term ARMv7-M?

For embedded applications, including as microcontrollers, and automotive body systems. Industrial control systems, and wireless networking, the Cortex-M3 processor is the first ARM processor based on the ARMv7-M architecture. Δ Contact Us :- trendblog.guest@gmail.com